高周波圧電共振器の課題を解消する回路技術を開発

DX/IoT/AI 無料IoT時代に向けた無線通信システムの小型化・低コスト化・高速化を実現へ

東京工業大学 科学技術創成研究院 未来産業技術研究所の伊藤浩之准教授、益一哉教授らはNICTと共同で、高周波圧電共振器を位相同期回路(PLL)に用いるための新しいアルゴリズムと回路技術を開発したと発表した(6月15日)。従来のPLLに比べ、低雑音かつ優れた性能指数(FoM)で動作することを確認したという。

この技術により、従来の無線モジュールで小型化・低コスト化のネックになっている水晶発振器を高周波圧電共振器に置き換えることができ、IoT時代に向けた無線通信システムの小型化・低コスト化・高速化に大きく貢献できる。高周波圧電共振器は小型で集積化でき、Q値に優れており、これを用いた発振器は優れたジッタ特性を有する。高周波圧電共振器は水晶共振器に比べ共振周波数のばらつきや温度依存性が大きいことが課題だったが、新規のアルゴリズムであるチャネル調整技術を用いたPLLの開発により課題を解決した。

成果の適用効果についての概念図

最小配線幅65nmのシリコンCMOSプロセスで試作、最高約9GHzの周波数出力をわずか180フェムト秒の位相ゆらぎで達成した。消費電力は12.7mW。この性能はPLLの性能指数 (FoM)で-244dBに相当し、小数点分周(フラクショナルN)PLLとしては世界トップクラスの性能である。無線通信システムの小型化・低コスト化、高速化に貢献できる。

成果は6月14日からハワイで開催される「The 2016 Symposium on VLSI Circuits」で現地時間6月17日に発表される。

研究背景

近年の無線通信システムでは、必要な機能の大部分が集積回路チップ上に実装されている。一方で、周波数基準信号(参照信号)を生成するために水晶共振器がいまだに個別の部品として用いられており、これらがモジュールの小型化・低コスト化のボトルネックになっている。多くのシステムでは、32kHzのクロックを生成する水晶発振器と、無線通信用のPLLの基準信号となる数十MHzのクロックを生成するために水晶発振器が用いられている。

これらを集積回路内の発振器や、集積化可能なMEMS素子を利用した発振器で置き換えるための研究開発が行われている。数十MHzのクロックについては、高Q・高安定なMEMS素子を使った発振器で置き換える手法が検討されている。しかし、無線通信用途では、周波数の安定性や精度に加えて信号の時間軸の揺らぎであるジッタが小さいことが求められるため技術的ハードルが高く、水晶発振器の代替となる実用的な発振器技術は実現していない。

一方、低ジッタな発振器技術として、GHz帯で動作する高Qな圧電共振器を利用する手法が提案されており、極めて優れた性能が実現できている。また、MEMS技術で作成する一部の圧電共振器は集積化できるため、水晶発振器が抱える実装上の課題も解決できる。しかし、製造工程や電源電圧・温度の変化に起因する周波数ばらつき(PVTばらつき)が発振器の周波数可変レンジよりも一般的に広いため、ターゲット周波数の信号が得られない可能性があることが実用上の課題だった。

研究成果

伊藤准教授らは、これらの問題を解決するための新規アルゴリズムであるチャネル調整技術と、それを用いたPLL(図1)を開発した。

図1:開発したPLLのブロック図

この技術は2つのPLLを接続したカスケードPLLの構成を利用する。まず、高い周波数分解能を有する初段PLLが、フィードバック制御がかかっていない自走状態で発振器の周波数を測定し、圧電共振器帯域内で動作できるように出力周波数を決定する。その後、フィードバック制御を行い、その目標周波数にロックさせる。

後段PLLの参照信号は前段PLLから供給されるが、その周波数情報はアナログ信号(図1中のf1st)とデジタル信号(N2nd)で、位相情報はアナログ信号(f1st)で伝えられる。周波数チューニングレンジが広い後段のPLLは、初段PLLの圧電共振器の周波数ばらつきを補正するようにデジタル信号(N2nd)を使って周波数逓倍比を設定する。このような自動的に動作周波数レンジ(チャネル)を割り振るアルゴリズムがチャネル調整技術であり、製造ばらつきや温度依存性が比較的大きい圧電共振器も利用できるようになる。また、ばらつきが大きい圧電共振器が利用できる以外に、以下のメリットがある。

- 初段PLLのアナログ出力信号f1st(後段PLLの位相参照信号)の位相雑音は、それが圧電共振器を用いた発振器で決まるように設計することで極めて小さくできる。さらに、この参照信号の周波数は高いため、後段PLLのループ帯域を広く設計できる。したがって、後段PLL出力信号の位相雑音の大部分が初段PLLの位相雑音で決まるように設計できるため、最終的な出力信号の位相雑音を小さくできる。また、参照信号の周波数が高いため、後段PLLのループフィルタの物理的サイズを小さくできる。

- 初段PLLは32kHzの参照信号で低速動作するため、小さい電力で高ビットのΔΣ変調器が利用できる。本回路では20bitのΔΣ変調器を使用しているため、1ppb以下の周波数分解能が理論上実現できる。

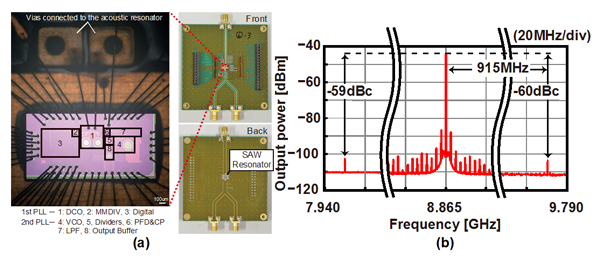

図2:チップ写真と出力信号スペクトラム

同回路は、最小配線半ピッチ65nm(ナノメートル)のシリコンCMOSプロセスで試作した(図2)。

図3:位相雑音の測定結果

図4:従来のフラクショナルN PLLとの性能比較

図5:従来のフラクショナルN PLLとのFoM比較

同回路は約9GHzの信号を出力し、180fsのRMSジッタを12.7mWの消費電力で実現した(図3)。これは-244dBのFoMに相当し、小数点分周(フラクショナルN)PLLとしては世界トップクラスの性能となる(図4、5)。

発表予定

この成果は、6月14日~17日にハワイで開催される「The 2016 Symposium on VLSI Circuits」のセッション「Session 22 — Clock and Frequency Synthesis」で発表する。講演タイトルは「An 8.865-GHz -244dB-FOM High-Frequency Piezoelectric Resonator-Based Cascaded Fractional-N PLL with Sub-ppb-Order Channel Adjusting Technique (サブppb級チャネル調整技術を用いた8.865GHz -244dB FOM高周波圧電共振器ベースカスケードフラクショナルN PLL)」となる。

論文著者

Sho Ikeda(池田翔、東工大 博士後期課程3年)、Hiroyuki Ito(伊藤浩之、東工大 准教授)、Akifumi Kasamatsu(笠松章史、NICT)、Yosuke Ishikawa(石川洋介、東工大 博士後期課程1年)、Takayoshi Obara(小原崇義、東工大 修士課程2年)、Naoki Noguchi(野口直記、東工大 修士課程2年)、Koji Kamisuki (紙透航志、東工大 修士課程2年)、Yao Jiyang(東工大 昨年度修了)、Shinsuke Hara(原紳介、NICT)、Dong Ruibing(董鋭冰、NICT)、Shiro Dosho(道正志郎、東工大 特任教授)、Noboru Ishihara(石原昇、東工大 特任教授)、Kazuya Masu(益一哉、東工大 教授)